# **DO Qualification Kit**

Model-Based Design Workflow for DO-178C

#### How to Contact MathWorks

www.mathworks.com

comp.soft-sys.matlab

www.mathworks.com/contact TS.html Technical Support

Web

Newsgroup

suggest@mathworks.com bugs@mathworks.com

doc@mathworks.com

service@mathworks.com info@mathworks.com

Product enhancement suggestions

Bug reports

Documentation error reports

Order status, license renewals, passcodes Sales, pricing, and general information

508-647-7000 (Phone)

508-647-7001 (Fax)

The MathWorks, Inc. 3 Apple Hill Drive Natick. MA 01760-2098

For contact information about worldwide offices, see the MathWorks Web site.

DO Qualification Kit Model-Based Design Workflow for DO-178C

© COPYRIGHT 2010–2012 by The MathWorks, Inc.

The software described in this document is furnished under a license agreement. The software may be used or copied only under the terms of the license agreement. No part of this manual may be photocopied or reproduced in any form without prior written consent from The MathWorks, Inc.

FEDERAL ACQUISITION: This provision applies to all acquisitions of the Program and Documentation by, for, or through the federal government of the United States. By accepting delivery of the Program or Documentation, the government hereby agrees that this software or documentation qualifies as commercial computer software or commercial computer software documentation as such terms are used or defined in FAR 12.212, DFARS Part 227.72, and DFARS 252.227-7014. Accordingly, the terms and conditions of this Agreement and only those rights specified in this Agreement, shall pertain to and govern the use, modification, reproduction, release, performance, display, and disclosure of the Program and Documentation by the federal government (or other entity acquiring for or through the federal government) and shall supersede any conflicting contractual terms or conditions. If this License fails to meet the government's needs or is inconsistent in any respect with federal procurement law, the government agrees to return the Program and Documentation, unused, to The MathWorks, Inc.

#### **Trademarks**

MATLAB and Simulink are registered trademarks of The MathWorks, Inc. See www.mathworks.com/trademarks for a list of additional trademarks. Other product or brand names may be trademarks or registered trademarks of their respective holders.

#### **Patents**

MathWorks products are protected by one or more U.S. patents. Please see www.mathworks.com/patents for more information.

#### **Revision History**

| September 2010 | Online only | New for Version 1.3 (Release 2010b)     |

|----------------|-------------|-----------------------------------------|

| April 2011     | Online only | Revised for Version 1.4 (Release 2011a) |

| September 2011 | Online only | Revised for Version 1.5 (Release 2011b) |

| March 2012     | Online only | Revised for Version 1.6 (Release 2012a) |

| September 2012 | Online only | Revised for Version 2.0 (Release 2012b) |

## **Tool Description**

| Overview of the Tools                                                                                                                                                                                                                                | 1-2                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Independence of the Tools                                                                                                                                                                                                                            | 1-3                             |

| Model and Source Code Development and Verification                                                                                                                                                                                                   | 1-10                            |

| Potential Tool Errors and Detection                                                                                                                                                                                                                  | 1-13                            |

| Object Code Development and Verification                                                                                                                                                                                                             | 1-18                            |

| Test Case Development                                                                                                                                                                                                                                | 1-20                            |

| DO-178C Software Life C                                                                                                                                                                                                                              | ycle                            |

| DO-178C Software Life C                                                                                                                                                                                                                              | ycle                            |

|                                                                                                                                                                                                                                                      |                                 |

| DO-178C Software Life Cycle Overview                                                                                                                                                                                                                 | 2-2                             |

| DO-178C Software Life Cycle Overview                                                                                                                                                                                                                 | 2-2<br>2-3                      |

| DO-178C Software Life Cycle Overview                                                                                                                                                                                                                 | 2-2<br>2-3<br>2-5               |

| DO-178C Software Life Cycle Overview  Model-Based Design Workflow in DO-178C  Software Planning Process  Activities of the Software Lifecycle Processes are Defined Software Life Cycle is Defined                                                   | 2-2<br>2-3<br>2-5<br>2-6        |

| DO-178C Software Life Cycle Overview  Model-Based Design Workflow in DO-178C  Software Planning Process  Activities of the Software Lifecycle Processes are Defined                                                                                  | 2-2<br>2-3<br>2-5<br>2-6<br>2-7 |

| DO-178C Software Life Cycle Overview  Model-Based Design Workflow in DO-178C  Software Planning Process  Activities of the Software Lifecycle Processes are Defined  Software Life Cycle is Defined  Software Life-Cycle Environment Is Selected and | 2-2 2-3 2-5 2-6 2-7 2-8 2-8 2-8 |

| Development and Revision of Software Plans are                                                            |      |

|-----------------------------------------------------------------------------------------------------------|------|

| Coordinated                                                                                               | 2-9  |

| Software Development Process                                                                              | 2-10 |

| High-Level Requirements are Developed                                                                     | 2-13 |

| Derived High-Level Requirements are Defined and                                                           | _ 10 |

| Provided to System Processes                                                                              | 2-13 |

| Software Architecture Is Developed                                                                        | 2-13 |

| Low-Level Requirements are Developed                                                                      | 2-14 |

| Derived Low-Level Requirements are Defined and Provided                                                   |      |

| to the System Processes                                                                                   | 2-14 |

| Source Code Is Developed                                                                                  | 2-14 |

| Executable Object Code and Parameter Data Item Files are                                                  |      |

| Produced and Loaded in the Target Computer                                                                | 2-14 |

| Specification Model Elements That Do Not Contribute                                                       |      |

| to Implementation or Realization of Any High-Level                                                        |      |

| Requirements are Identified                                                                               | 2-15 |

| Design Model Elements That Do Not Contribute to                                                           |      |

| Implementation or Realization of Any Software                                                             | 0.15 |

| Architecture are Identified                                                                               | 2-15 |

| Design Model Elements That Do Not Contribute to                                                           |      |

| Implementation or Realization of Any Low-Level                                                            | 0.15 |

| Requirements are Identified                                                                               | 2-15 |

| Verification of Requirements Process                                                                      | 2-17 |

| High-Level Requirements Comply with System                                                                |      |

| Requirements                                                                                              | 2-19 |

| High-Level Requirements Are Accurate and Consistent<br>High-Level Requirements Are Compatible with Target | 2-19 |

| Computer                                                                                                  | 2-20 |

| High-Level Requirements Are Verifiable                                                                    | 2-20 |

| High-Level Requirements Conform to Standards                                                              | 2-21 |

| High-Level Requirements Are Traceable to System                                                           |      |

| Requirements                                                                                              | 2-22 |

| Algorithms Are Accurate                                                                                   | 2-22 |

| Simulation Cases Are Correct                                                                              | 2-23 |

| Simulation Procedures Are Correct                                                                         | 2-23 |

| Simulation Results Are Correct and Discrepancies                                                          | 0 00 |

| Explained                                                                                                 | 2-23 |

| Verification of Design Process                                                                            | 2-24 |

| Low-Level Requirements Comply with High-Level                                                             |      |

| Requirements                                                                                              | 9_96 |

| Low-Level Requirements Are Compatible with Tomputer  Low-Level Requirements Are Verifiable  Low-Level Requirements Conform to Standards  Low-Level Requirements Are Traceable to High  Requirements                                                                                                                                                                                                                                                                                              |                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| Low-Level Requirements Are Verifiable<br>Low-Level Requirements Conform to Standards<br>Low-Level Requirements Are Traceable to High                                                                                                                                                                                                                                                                                                                                                             |                                                 |

| Low-Level Requirements Conform to Standards<br>Low-Level Requirements Are Traceable to High                                                                                                                                                                                                                                                                                                                                                                                                      |                                                 |

| Low-Level Requirements Are Traceable to High                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                 |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                 |

| Dogginamenta                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -Level                                          |

| Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                 |

| Algorithms Are Accurate                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                 |

| Software Architecture Is Compatible with High-                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -Level                                          |

| Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                 |

| Software Architecture Is Consistent                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                 |

| Software Architecture Is Compatible with Targe                                                                                                                                                                                                                                                                                                                                                                                                                                                   | et                                              |

| Computer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                 |

| Software Architecture Is Verifiable                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                 |

| Software Architecture Conforms to Standards .                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                 |

| Software Partitioning Integrity Is Confirmed                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                 |

| Simulation Case Are Correct                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                 |

| Simulation Procedures Are Correct                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                 |

| Simulation Results Are Correct and Discrepance                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ies                                             |

| Source Code Complies with Low-Level Requirem Source Code Complies with Software Architectur Source Code Is Verifiable                                                                                                                                                                                                                                                                                                                                                                            | ss<br>nents                                     |

| erification of Coding and Integration Process Source Code Complies with Low-Level Requirems Source Code Complies with Software Architectur Source Code Is Verifiable                                                                                                                                                                                                                                                                                                                             | ss nents nents nents ete eved                   |

| Explained                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ss nents nents nete and ete eved epancies       |

| erification of Coding and Integration Process Source Code Complies with Low-Level Requirem Source Code Complies with Software Architectur Source Code Is Verifiable Source Code Conforms to Standards Source Code Is Traceable to Low-Level Requirem Source Code Is Accurate and Consistent Output of Software Integration Process Is Comp Correct Parameter Data Item File Is Correct and Comple Verification of Parameter Data Item File Is Achi Formal Analysis Cases and Procedures Are Corr | nents nents nents nents elete and eved epancies |

| Executable Object Code Complies with Low-Level             |          |

|------------------------------------------------------------|----------|

| Requirements                                               | 2-4      |

| Executable Object Code Is Robust with Low-Level            |          |

| Requirements                                               | 2-4      |

| Executable Object Code Is Compatible with Target           |          |

| Computer                                                   | 2-4      |

|                                                            |          |

| Verification of Verification Process Results               | 2-4      |

| Test Procedures Are Correct                                | 2-8      |

| Test Results Are Correct and Discrepancies Explained       | 2-       |

| Test Coverage of High-Level Requirements Is Achieved       | 2-       |

| Test Coverage of Low-Level Requirements Is Achieved        | 2-       |

| Test Coverage of Software Structure (Modified              |          |

| Condition/Decision) Is Achieved                            | 2-       |

| Test Coverage of Software Structure (Decision Coverage) Is | 3        |

| Achieved                                                   | 2-       |

| Test Coverage of Software Structure (Statement Coverage)   |          |

| Is Achieved                                                | 2-       |

| Test Coverage of Software Structure (Data Coupling and     |          |

| Control Coupling) Is Achieved                              | 2-       |

| Verification of Additional Code That Cannot Be Traced to   |          |

| Source Code Is Achieved                                    | 2-       |

| Simulation Cases Are Correct                               | 2-       |

| Simulation Procedures Are Correct                          | 2-       |

| Simulation Results Are Correct and Discrepancies           |          |

| Explained                                                  | 2-       |

| Formal Analysis Cases and Procedures Are Correct           | 2-       |

| Formal Analysis Results Are Correct and Discrepancies      |          |

| Explained                                                  | 2-       |

| Coverage of High-Level Requirements Is Achieved            | 2-       |

| Coverage of Low-Level Requirements Is Achieved             | 2-       |

| Verification Coverage of Software Structure Is Achieved    | 2-       |

| Verification of Property Preservation Between Source And   |          |

| Object Code                                                | 2-       |

| Formal Method Is Correctly Justified And Appropriate       | 2-       |

|                                                            |          |

| Software Configuration Management Process                  | 2-       |

| Configuration Items Are Identified                         | 2-       |

| Baselines and Traceability Are Established                 | 2-       |

| Problem Reporting, Change Control, Change Review, and      | 4-       |

| Configuration Status Accounting Are Established            | 2-       |

| Archive, Retrieval, and Release Are Established            | 2-<br>2- |

| Software Load Control Is Established                       | 2-<br>9- |

|                                                            |          |

| Software Life Cycle Environment Control Is Established                                                                                    | 2-59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Software Quality Assurance Process  Assurance Is Obtained That Software Plans and Standards are Daysland and Paviowed for Compliance With | 2-60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DO-178C and For Consistency                                                                                                               | 2-61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Comply with Approved Software Plans                                                                                                       | 2-61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Comply with Approved Software Standards                                                                                                   | 2-61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Software Life Cycle Processes are Satisfied                                                                                               | 2-62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Conducted                                                                                                                                 | 2-62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Certification Liaison Process                                                                                                             | 2-63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| and the Certification Authority Is Established  The Means of Compliance Is Proposed and Agreement                                         | 2-63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Obtained                                                                                                                                  | 2-64<br>2-64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Acron                                                                                                                                     | yms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Acronyms                                                                                                                                  | A-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Referen                                                                                                                                   | <u>ices</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Normative References                                                                                                                      | B-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                           | Assurance Is Obtained That Software Plans and Standards are Developed and Reviewed for Compliance With DO-178C and For Consistency  Assurance is Obtained That Software Life Cycle Processes Comply with Approved Software Plans  Assurance is Obtained That Software Life Cycle Processes Comply with Approved Software Standards  Assurance is Obtained That Transition Criteria for the Software Life Cycle Processes are Satisfied  Assurance is Obtained That Software Conformity Review is Conducted  Certification Liaison Process  Communication and Understanding Between the Applicant and the Certification Authority Is Established  The Means of Compliance Is Proposed and Agreement with the Plan for Software Aspects of Certification is Obtained  Compliance Substantiation Is Provided  Acron  Acron  Referen |

# Tool Description

- "Overview of the Tools" on page 1-2

- "Independence of the Tools" on page 1-3

- "Model and Source Code Development and Verification" on page 1-10

- "Potential Tool Errors and Detection" on page 1-13

- "Object Code Development and Verification" on page 1-18

- "Test Case Development" on page 1-20

### Overview of the Tools

The purpose of this section is to describe the high level architecture of the development and verification tools used in the DO-178C workflow with Model-Based Design. This section also describes the independence aspects of the various tools and how errors in the tools can be detected. There are two types of tools used in the workflow, development tools and verification tools.

#### Development tools are:

- Simulink®

- Stateflow®

- MATLAB® Coder<sup>TM</sup>

- Simulink Coder

- Embedded Coder®

#### Verification tools are:

- MATLAB Report Generator<sup>TM</sup>

- Simulink Report Generator

- Simulink Design Verifier<sup>TM</sup>

- Simulink Code Inspector<sup>TM</sup>

- Simulink Verification and Validation™ Model Advisor

- Simulink Verification and Validation Model Coverage

- SystemTest<sup>TM</sup>

- Polyspace®

### Independence of the Tools

Simulink and Stateflow are separate tools used for the development of models. Simulink may be used without Stateflow, but when Stateflow is used, Simulink is also required. Simulink and Stateflow are tightly integrated and are not independent of each other. There is not a requirement for Simulink and Stateflow to be independent since they are both used together as part of the development of the software design. The Simulink API, which is referenced throughout this document, provides an interface for other tools that cannot access the in memory data directly, to get the data from the model by using this interface. For example, a user can get data from a model using the get\_param command in MATLAB or set a parameter in the model using the set param command in MATLAB.

See the workflow section of this document, "Software Development Process" on page 2-10, which includes the following objectives for the use of Simulink and Stateflow:

- Software High-Level Requirements are Developed

- Derived Software High-Level Requirements are Developed

- Software Architecture is Developed

- Software Low-Level Requirements are Developed

- Derived Software Low-Level Requirements are Developed

MATLAB Coder, Simulink Coder and Embedded Coder are separate tools used for the development of source code. MATLAB Coder is a prerequisite for Simulink Coder and Embedded Coder. Simulink Coder is required when generating code from Simulink and Stateflow models. These three tools are tightly integrated and are not independent of each other. There is not a requirement for MATLAB Coder, Simulink Coder and Embedded Coder to be independent since they are used together as part of the development of the source code. In the following sections of this document, references to Embedded Coder are intended to include Simulink Coder and MATLAB Coder as the entire code generation tool set.

See the workflow section of this document, "Software Development Process" on page 2-10, which includes the following objectives for the use of MATLAB Coder, Simulink Coder and Embedded Coder:

#### • Source Code is Developed

The MATLAB and Simulink Report Generators are two separate tools, with the MATLAB Report Generator being a prerequisite for the Simulink Report Generator. The Simulink Report Generator provides components for reporting on Simulink and Stateflow models and is integrated with the MATLAB Report Generator. These components interrogate the model using the Simulink API to read data from the model loaded in memory. The report generator components used to generate the System Design Description document can only read data from the model, they do not have the capability to write or modify data in the model. The System Design Description includes requirements traceability links that may be inserted into the models using the Requirements Management Interface that is part of Simulink Verification and Validation.

See the workflow sections of this document, "Verification of Requirements Process" on page 2-17 and "Verification of Design Process" on page 2-24, which includes the following objectives for the use of MATLAB Report Generator and Simulink Report Generator:

- Verification of Requirements Process

- Software High-Level Requirements Comply with System Requirements

- High-Level Requirements are Accurate and Consistent

- High-Level Requirements are Compatible with Target Computer

- High-Level Requirements are Verifiable

- High-Level Requirements Conform to Standards

- High-Level Requirements are Traceable to System Requirements

- Algorithms are Accurate

- Verification of Design Process

- Low-Level Requirements Comply with High-Level Requirements

- Low-Level Requirements are Accurate and Consistent

- Low-Level Requirements are Compatible with Target Computer

- Low-Level Requirements are Verifiable

- Low-Level Requirements Conform to Standards

- Low-Level Requirements are Traceable to System Requirements

- Algorithms are Accurate

- Software Architecture is Compatible with High-Level Requirements

- Software Architecture is Consistent

- Software Architecture is Compatible with Target Computer

- Software Architecture is Verifiable

- Software Architecture is Conforms to Standards

Simulink Design Verifier is a separate tool with three capabilities; Design Error Detection, Property Proving and Test Case Generation. Simulink Design Verifier contains formal analysis engines that operate on an internal representation derived from but in a different form than the Simulink model loaded in memory. Design Error Detection can find specific design errors in the model, such as divide-by-zero or numeric overflows, using formal methods. Property Proving, which also uses formal methods, can prove properties that are defined by the user in conjunction with assumptions that are also defined by the user. The formal analysis engines are separate and independent of Simulink and Stateflow, and do not involve simulation of the model. Simulink Design Verifier can automatically generate test cases based on the model that can be used to verify the executable object code complies with the model. The basis for the test cases can be a combination of user defined constraints, model coverage criteria for blocks in the model and user defined test objectives. The constraint blocks, model coverage criteria and test objective blocks are ignored by Embedded Coder and are therefore independent of the coding process. In order to verify the code using the generated test cases, the test cases must be run on the model in order to produce expected results for the code. The completeness of those test cases may be assessed using the model coverage tool and the expected results may be assessed via review of the results from simulation.

See the workflow sections of this document, "Verification of Requirements Process" on page 2-17, "Verification of Design Process" on page 2-24 and "Testing of Outputs of Integration Process" on page 2-40, which includes the following objectives for the use of Simulink Design Verifier:

- Verification of Requirements Process

- Software High-Level Requirements Comply with System Requirements

- High-Level Requirements are Verifiable

- Algorithms are Accurate

- Verification of Design Process

- Low-Level Requirements Comply with High-Level Requirements

- Low-Level Requirements are Verifiable

- Algorithms are Accurate

- Testing of Outputs of Integration Process

- Executable Object Code Complies with Low-Level Requirements

- Executable Object Code is Robust with Low-Level Requirements

Simulink Code Inspector is a separate tool that can be used to verify source code developed from Embedded Coder. This tool is implemented independent of Simulink, Stateflow and Embedded Coder. This tool interrogates the model using the Simulink API to read data from the model loaded in memory. All of the API commands used can only read data from the model, they do not have the capability to write or modify data in the model. The model is converted into a different intermediate representation for use in the code inspection process. The Simulink Code Inspector also uses the generated C code files as input and parses these into a different intermediate representation that can be compared to the model's intermediate representation. The requirements, design and source code for Simulink Code Inspector are developed separately and are independent of MATLAB Coder, Simulink Coder and Embedded Coder implementations.

See the workflow section of this document, "Verification of Coding and Integration Process" on page 2-35, which includes the following objectives for the use of Simulink Code Inspector:

- Source Code Complies with Low-Level Requirements

- Source Code Complies with Software Architecture

- Source Code is Verifiable

- Source Code is Traceable to Low-Level Requirements

- Source Code is Accurate and Consistent

The Model Advisor checks are provided in several different products; Simulink, Embedded Coder, Simulink Code Inspector, Simulink Verification and Validation and Simulink Control Design™. The basic core implementation of Model Advisor checks is done via an engine that uses MATLAB functions and is independent of Simulink, Stateflow and Embedded Coder. The Model Advisor uses the Simulink API to read data from the model loaded in memory. The Model Advisor does have the capability to automatically fix issues detected by checks, but the fixes must be initiated by the user and the model would have to be resaved. Then the checks can be re-run by the user in order to verify the fixes. For custom checks created by the user, it is the user's responsibility to not allow those checks to modify the model.

See the workflow sections of this document, "Verification of Requirements Process" on page 2-17 and "Verification of Design Process" on page 2-24, which includes the following objectives for the use of Model Advisor:

- Verification of Requirements Process

- High-Level Requirements are Accurate and Consistent

- High-Level Requirements are Compatible with Target Computer

- High-Level Requirements Conform to Standards

- High-Level Requirements are Traceable to System Requirements

- Algorithms are Accurate

- Verification of Design Process

- Low-Level Requirements are Accurate and Consistent

- Low-Level Requirements are Compatible with Target Computer

- Low-Level Requirements Conform to Standards

- Low-Level Requirements are Traceable to System Requirements

- Algorithms are Accurate

- Software Architecture is Consistent

- Software Architecture is Compatible with Target Computer

Software Architecture is Conforms to Standards

The Model Coverage capability is provided as part of Simulink Verification and Validation. Model Coverage instruments the model loaded into memory prior to simulation and evaluates the coverage criteria as the simulation progresses. Model Coverage also has the capability to merge multiple simulation runs into a combined coverage report. The user can run simulations with coverage enabled and disabled to insure there has been no effect on behavior of the model due to the instrumentation.

See the workflow sections of this document, "Verification of Requirements Process" on page 2-17 and "Verification of Design Process" on page 2-24, which includes the following objectives for the use of Model Coverage:

- Verification of Requirements Process

- Software High-Level Requirements Comply with System Requirements

- High-Level Requirements are Verifiable

- Verification of Design Process

- Low-Level Requirements Comply with High-Level Requirements

- Low-Level Requirements are Verifiable

SystemTest is a separate tool that can be used to execute simulations in a batch model and check actual results against expected results. It also provides the capability to author test cases manually or to import test cases in other formats, such as Excel® spreadsheets. Because the test cases and expected results are developed manually by the user, they are independent of the model and source code. The Limit Check element within SystemTest that is used to determine Pass/Fail of the model or code under test is implemented completely independent of Simulink, Stateflow and Embedded Coder.

See the workflow sections of this document, "Verification of Requirements Process" on page 2-17 and "Verification of Design Process" on page 2-24, which includes the following objectives for the use of SystemTest:

- Verification of Requirements Process

- Software High-Level Requirements Comply with System Requirements

- High-Level Requirements are Accurate and Consistent

- High-Level Requirements are Verifiable

- Algorithms are Accurate

- Verification of Design Process

- Low-Level Requirements Comply with High-Level Requirements

- Low-Level Requirements are Accurate and Consistent

- Low-Level Requirements are Verifiable

- Algorithms are Accurate

- Software Architecture is Compatible with High-Level Requirements

- Software Architecture is Consistent

- Software Architecture is Verifiable

Polyspace is a separate tool that has two capabilities; coding standards checking (example MISRA C®) and run time error detection. The main input to Polyspace is the source code; however it can optionally read range specification data from the model using the Simulink API. When using the Polyspace Model Link™ SL product, it can trace defects found in the source code back to the source blocks in the model. Polyspace is completely independent of MATLAB Coder, Simulink Coder and Embedded Coder. The requirements, design and source code for Polyspace are developed separately and are independent of MATLAB Coder, Simulink Coder and Embedded Coder implementations. Polyspace also supports C code, whether it is automatically generated or manually developed. For run-time error detection, Polyspace uses Abstract Interpretation in its formal methods engine.

See the workflow section of this document, "Verification of Coding and Integration Process" on page 2-35, which includes the following objectives for the use of Polyspace:

- Source Code is Verifiable

- Source Code Conforms to Standards

- Source Code is Accurate and Consistent

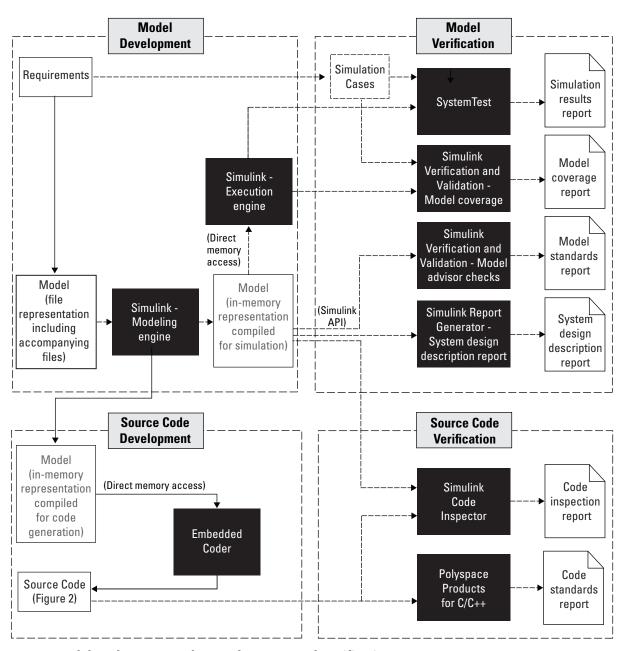

## **Model and Source Code Development and Verification**

In a workflow where code is generated from the Simulink and Stateflow models, the models are considered to be the low-level software requirements and architecture as defined in DO-178C. The actual low-level requirements are the compiled model in memory as interpreted by the Simulink engine based on input from the model file, as well as any data files, such as MATLAB or MAT files that load data into the MATLAB or model workspaces. See Figure 1: Model and Source Code Development and Verification on page 1-12. The model file itself does not represent the low-level requirements, because the model semantics are not fully included in that file. The model semantics are not complete until the model file has been loaded into memory and the Simulink engine has compiled the model. Some of the model semantics that are determined at compile time, but are not included in the model file, for the model consists of:

- Propagated Sample Times

- Propagated Data Types

- Propagated Signal Dimensions

- Propagated Signal Types

- Block Execution Order

The System Design Description, which is created using the Simulink Report Generator, provides a document that details the compiled for simulation in memory representation of the model. This provides documentation of the low-level software requirements, as defined in the DO-178C glossary:

Low-level requirements – Software requirements developed from high-level requirements, derived requirements, and design constraints from which Source Code can be directly implemented without further information.<sup>1</sup>

Compile for simulation and compile for code generation are two different compiles and result in two slightly different in-memory representations. SystemTest, Model Coverage, Simulink Code Inspector, Model Advisor and Report Generator only compile for simulation. Embedded Coder compiles for

<sup>&</sup>quot;Software Considerations in Airborne Systems and Equipment Certification," Document No. RTCA DO-178C, December 13, 2011, Prepared by SC-205

code generation, which includes the entire compile for simulation information plus the following additional information.

- Model optimizations that are applied only for code generation

- Consistency checking for storage classes in the generated code

Since the model and code verification activities may take place at different times or on different computers, it is necessary to check the consistency of the in-memory representations of the model. An MD5 Checksum computation is used to check this consistency. The MD5 checksum is computed based on the in-memory representation and includes any data that has been loaded into the workspace from external files that are used by the model. The MD5 Checksum value is automatically inserted into the Model Advisor report, the System Design Description and the Simulink Code Inspector report. It is also possible to use the Simulink API to access the MD5 Checksum and insert it into a SystemTest report or for use in other reports that may be generated during simulations using other methods such as Report Generator or MATLAB scripts. A model version number and last saved date are also available in the reports, and this data is automatically updated each time that a model is saved. The model version number and last saved dates are not affected by externally loaded data, so that is why the MD5 Checksum is required to verify complete consistency of the in-memory representation. The System Design Description does document the workspace variables that are used by the model at the time the report is generated.

Figure 1: Model and Source Code Development and Verification

## **Potential Tool Errors and Detection**

The following table provides information regarding potential user and tool errors, the effects of those errors and how the errors are detected.

| Error Source                                          | Error Effect                        | Detected By                                                                             | Mitigating<br>Factors                                     |

|-------------------------------------------------------|-------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------|

| User Input<br>(model,<br>MATLAB, or<br>MAT file data) | Failure to comply with requirements | Simulation<br>Cases and review<br>of System Design<br>Description                       | SystemTest<br>and Report<br>Generator<br>Qualification    |

|                                                       | Failure to conform to standards     | Model Advisor<br>and review of<br>System design<br>Description                          | Model Advisor<br>and Report<br>Generator<br>Qualification |

|                                                       | Unintended function                 | Review of System Design Description, Simulation Cases and Model Coverage                | SystemTest and<br>Model Coverage<br>Qualification         |

| Simulink Engine                                       | Failure to comply with requirements | Simulation<br>Cases and review<br>of System Design<br>Description                       | SystemTest<br>and Report<br>Generator<br>Qualification    |

|                                                       | Failure to conform to standards     | Model Advisor<br>and review of<br>System design<br>Description                          | Model Advisor<br>and Report<br>Generator<br>Qualification |

|                                                       | Unintended<br>function              | Review of<br>System Design<br>Description,<br>Simulation<br>Cases and Model<br>Coverage | SystemTest and<br>Model Coverage<br>Qualification         |

| Error Source                                                                              | Error Effect                                        | Detected By                                                                  | Mitigating<br>Factors                           |  |

|-------------------------------------------------------------------------------------------|-----------------------------------------------------|------------------------------------------------------------------------------|-------------------------------------------------|--|

| Model Advisor                                                                             | Model Advisor Incorrect model standards reporting   |                                                                              | Model Advisor<br>and Polyspace<br>Qualification |  |

| Report<br>Generator                                                                       | Incorrect<br>System Design<br>Description           | Review of<br>System Design<br>Description<br>and resolution<br>activity      | Report<br>Generator<br>Qualification            |  |

| Embedded Coder                                                                            | Incorrect source code                               | Review of<br>Simulink Code<br>Inspector Report                               | Simulink Code<br>Inspector<br>Qualification     |  |

| Simulink Code Inspector Inspector Inspector Incorrect reported failure of the source code |                                                     | Review of<br>Simulink Code<br>Inspector Report<br>and resolution<br>activity | Simulink Code<br>Inspector<br>Qualification     |  |

| Polyspace                                                                                 | Incorrect<br>reported failure<br>of the source code | Review of<br>Polyspace Report<br>and resolution<br>activity                  | Polyspace<br>Qualification                      |  |

The only errors that can directly affect both the model and the source code are user input errors or Simulink Engine errors. In either of these cases the result is incorrect low-level software requirements. The incorrect low-level software requirements are detectable at the model level via a combination of design reviews, simulation, model coverage assessment and conformance to standards checking. Because these activities are being done on the compiled in memory model, the detection is effective whether the error is based on user input or the Simulink Engine. Additionally, if the software level is A or B, the

simulation cases used to verify behavior, must be developed by a person other than the model developer in order to achieve independence requirements.

Once the model has been verified, the source code can be generated by Embedded Coder and verified by Simulink Code Inspector and Polyspace. The three tools are developed by independent groups with MathWorks and have independent requirements and code. The one exception is that Simulink Code Inspector and Polyspace do share a common parser function for the C code, but Embedded Coder does not contain this functionality. The Simulink Code Inspector uses the Simulink API as input source for the model information. This is the same API used by Model Advisor and the Simulink Report Generator. This API is verified during the tool qualification testing process for each of these tools. The Simulink Code Inspector input from the model is based on the compiled for simulation in memory representation and does not have access to the compiled for code generation additional information. Both Simulink Code Inspector and Polyspace read the code and header files that are output from Embedded Coder directly as ASCII text files.

The following model verification tools may be qualified, per DO-178C guidelines, using the DO Qualification Kit:

- Simulink Report Generator System Design Description

- Simulink Verification and Validation Model Advisor DO-178C/DO-331 Checks

- Simulink Verification and Validation Model Coverage Coverage and Complexity Reporting

- SystemTest Limit Check Element

Additionally, the following code verification tools may be qualified, per DO-178C guidelines, using the DO Qualification Kit:

- Simulink Code Inspector Verification of compliance and traceability to the model

- Polyspace Conformance to standards and run-time error detection

To summarize, all tool errors in the workflow are detectable by one or more verification activities. Additionally, the tool qualification process for the

verification tools provides a level of confidence in the tools that is equivalent to manual verification activities that are automated by the tools.

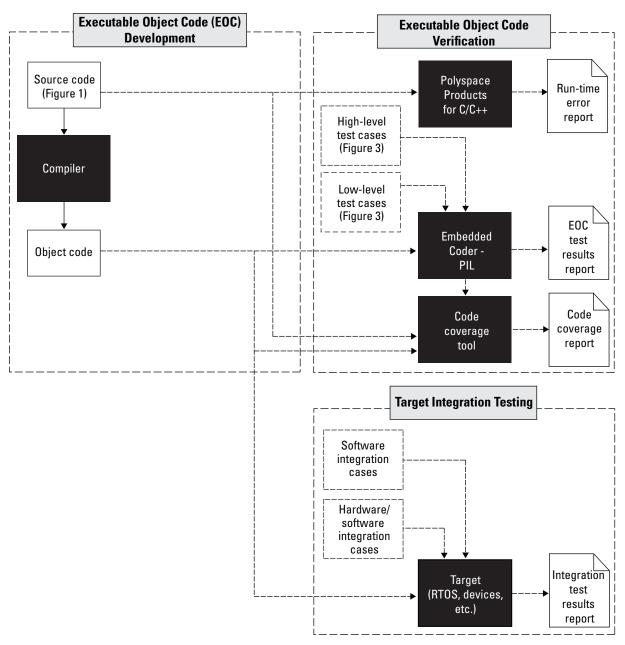

## **Object Code Development and Verification**

Figure 2: Executable Object Code Development and Verification on page 1-19 shows the Executable Object Code development and verification activities, including the use of Processor In-The-Loop (PIL) mode and target integration testing. These activities are downstream of the model and source code development and verification activities. The compiler is a third party tool that is not provided by MathWorks and therefore is independent. Errors injected by the compiler are detectable by the testing process. The code coverage tool is also provided by a third party, rather than MathWorks<sup>®</sup>, and this tool is normally qualified.

Figure 2: Executable Object Code Development and Verification

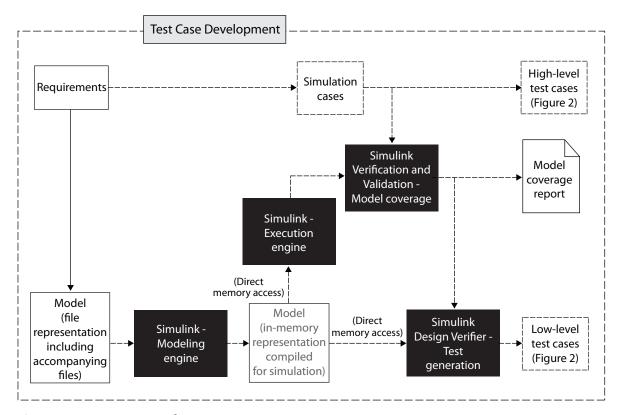

### **Test Case Development**

The DO-178C standard calls out three types of testing, all of which are based on the software requirements:

- Hardware/Software Integration Tests

- Software Integration Tests

- Low-Level Tests

Additionally, for DO-178C, test cases should include:

- Normal range test cases

- Robustness test cases

For the executable object code developed from models, the high level test cases and expected results can be the same as the simulation cases and expected results (see Figure 3: Test Case Development on page 1-21). These are developed from the high level requirements document and are completely independent of Simulink, Embedded Coder and the compiler used for the project. The test cases and expected result should also include robustness cases. These test cases can be executed using processor in-the-loop (PIL) capability in conjunction with the Simulink environment used as a test harness, or on a completely separate software test harness.

The low-level test cases and expected results are based on the models, which represent the low-level requirements. Simulink Design Verifier may be used to develop these test cases (see Figure 3). Simulink Design Verifier uses the model as its primary input and also has the capability to input model coverage data. DO-178C calls out that if it can be shown that high level tests cover low-level requirements, then those low-level requirements do not need to be covered by specific low level tests. Model coverage can be used as evidence that high level tests cover low-level requirements, in particular for logical decisions within the models, but also for lookup table data and signal range data within the models. Simulink Design Verifier can then be used to generate tests for the remaining low-level requirements that are not covered by high level testing, for example derived requirements within the model. The user can also insert signal constraints and user defined test objectives within the models or in model test harnesses to complete the testing. The use of test

objectives on the inputs to a model to insert test data beyond normal ranges is a good way to verify robustness, for example.

The Hardware/Software Integration cases and the Software Integration cases (see Figure 3) are typically developed manually based on the high-level software requirements. These test cases are executed on the final target in an environment independent of the modeling environment. The final target would include an RTOS or scheduler and the device drivers that interface to the target hardware.

Figure 3: Test Case Development

# DO-178C Software Life Cycle

- "DO-178C Software Life Cycle Overview" on page 2-2

- "Model-Based Design Workflow in DO-178C" on page 2-3

- "Software Planning Process" on page 2-5

- "Software Development Process" on page 2-10

- "Verification of Requirements Process" on page 2-17

- "Verification of Design Process" on page 2-24

- "Verification of Coding and Integration Process" on page 2-35

- "Testing of Outputs of Integration Process" on page 2-40

- "Verification of Verification Process Results" on page 2-48

- "Software Configuration Management Process" on page 2-57

- "Software Quality Assurance Process" on page 2-60

- "Certification Liaison Process" on page 2-63

## **DO-178C Software Life Cycle Overview**

The DO-178C software life cycle consists of the following processes:

- Planning

- Software development

- Verification of requirements

- Verification of design

- Verification of coding and integration

- Testing of outputs of integration

- Verification of verification results

- Software configuration management

- Software quality assurance

- Certification liaison process

There are objectives that must be met for each of the life cycle stages in DO-178C. In Annex A of DO-178C, these objectives are summarized in tables. This document summarizes those tables and provides recommendations on meeting the objectives using a Model-Based Design process. Available Model-Based Design tools that can be used in achieving the objectives are also included.

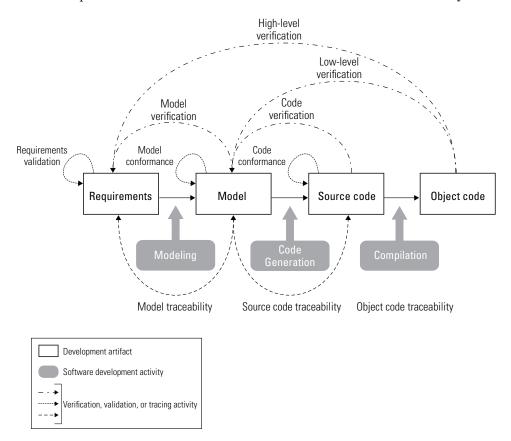

## Model-Based Design Workflow in DO-178C

The following diagram shows a Model-Based Design workflow that addresses the development and verification activities in a DO-178C software life cycle.

The following table lists the MathWorks products and capabilities that can be used in each activity of the workflow as Model-Based Design tools.

| Workflow Activity       | Available Products and Capabilities for Model-Based Design |  |  |

|-------------------------|------------------------------------------------------------|--|--|

| Requirements validation | Manual review                                              |  |  |

| Modeling                | Simulink, Stateflow                                        |  |  |

| Workflow Activity                             | Available Products and Capabilities for Model-Based Design                                                                                                                                                                                                                     |  |  |  |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Model traceability                            | Simulink Verification and Validation — Requirements Management<br>Interface (RMI), Simulink Report Generator — System Design<br>Description report*                                                                                                                            |  |  |  |

| Model conformance                             | Simulink Verification and Validation — DO-178C/DO-331 checks*                                                                                                                                                                                                                  |  |  |  |

| Model verification                            | SystemTest — Limit Check element*, Simulink Design Verifier — Property Proving (optional), Simulink Design Verifier — Design Error Detection (optional), Simulink Verification and Validation — Model Coverage*, Simulink Report Generator — System Design Description report* |  |  |  |

| Code generation                               | Embedded Coder                                                                                                                                                                                                                                                                 |  |  |  |

| Source code traceability                      | Simulink Code Inspector — Traceability Report*                                                                                                                                                                                                                                 |  |  |  |

| Code conformance                              | Polyspace Products for C/C++ — MISRA AC AGC checks*                                                                                                                                                                                                                            |  |  |  |

| Code verification                             | Simulink Code Inspector — Code Verification Report*, Polyspace Products for C/C++*                                                                                                                                                                                             |  |  |  |